Es hat sich jedoch gezeigt, dass bei SOT-MRAM mit senkrechter Magnetisierung die Schreibwahrscheinlichkeit bei hohem Strom einbrechen oder sogar oszillieren kann.

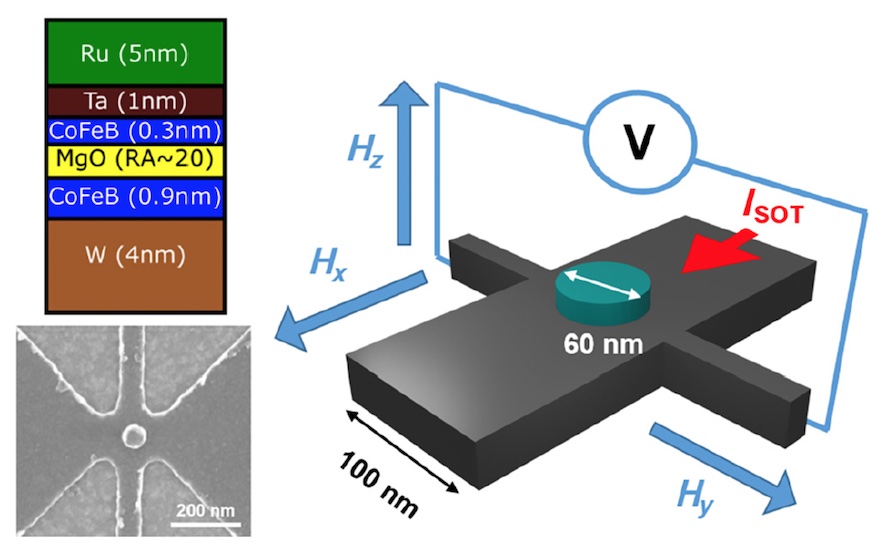

© CEA

Ein Team von SPINTEC hat in Zusammenarbeit mit dem aus dem Labor hervorgegangenen Unternehmen Antaios dieses schädliche Phänomen in SOT-MRAM-Bauteilen auf Basis von β-W/CoFeB/MgO-Schichten quantifiziert. Durch Messung der Schreibfehlerrate (Write Error Rate, WER) wurde nachgewiesen, dass dieses Phänomen nicht zufällig, sondern deterministisch ist.

Die Forscher führten sogenannte Makrospin-Simulationen (gleichmäßige Magnetisierung) durch, die auf experimentellen Parametern basieren. Diese Simulationen reproduzieren die WER-Karten und ermöglichen es, den Mechanismus zu erklären. Bei Injektion eines Stromimpulses mit hoher Amplitude neigt sich die Magnetisierung des SOT-MRAM in die Ebene, bei 90° zur ursprünglichen Richtung entlang der -z-Achse (entsprechend dem Bit 0).

Diese dynamische Position ist jedoch instabil, und am Ende des Impulses können während der Relaxation thermische Fluktuationen die Magnetisierung in die ursprüngliche Richtung -z zurückkehren lassen. Dies führt zu einem Schreibfehler, bei dem das Bit auf 0 bleibt, anstatt es in die Richtung +z zu orientieren, um das Bit auf 1 zu setzen.

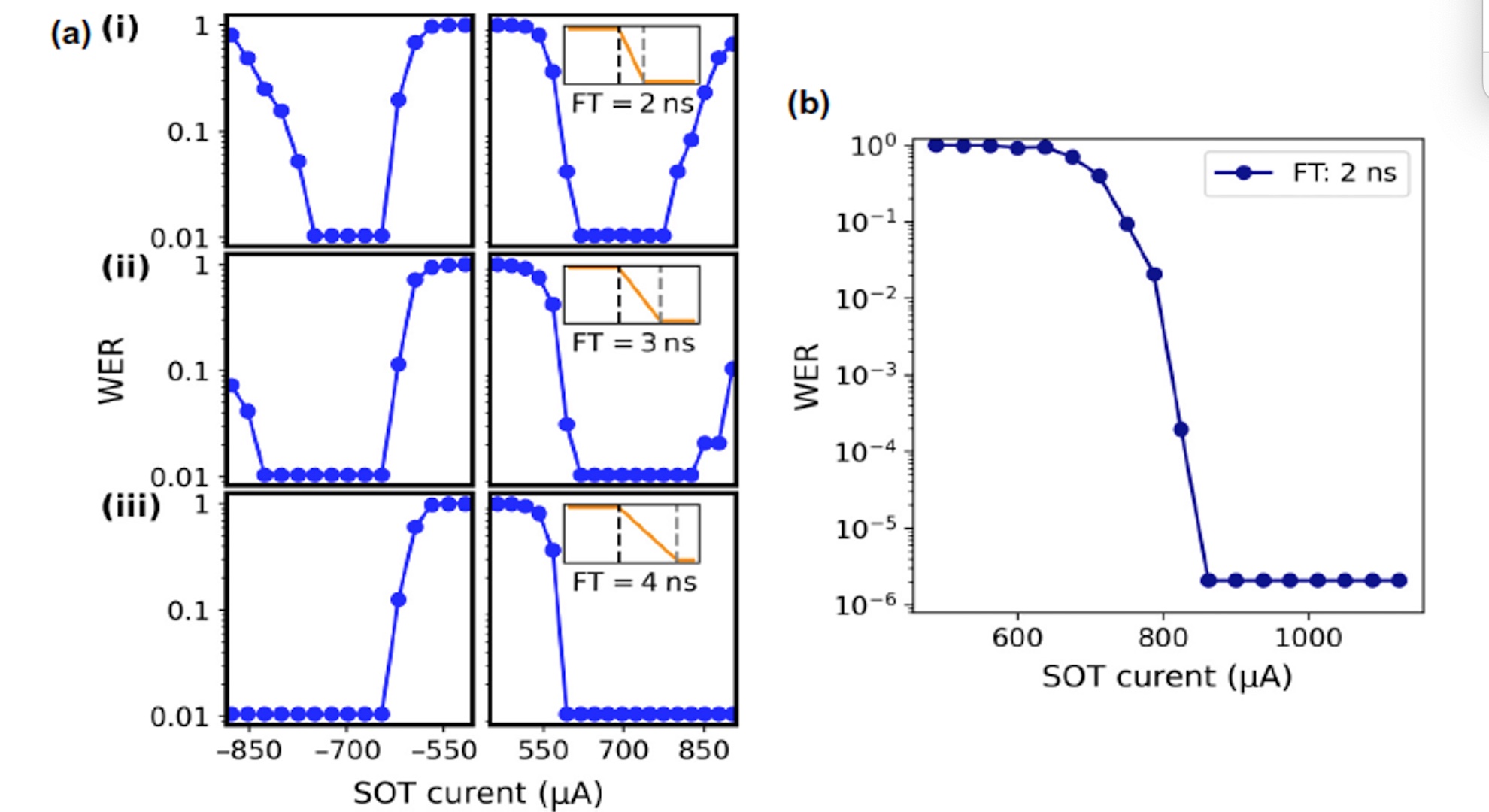

Die einfache Lösung, ohne auf exotische Materialien oder physikalische Effekte zurückgreifen zu müssen, besteht darin, die Form des Stromimpulses zu verändern. Durch Verlängerung der Abfallzeit des Impulses wirkt der Strom weiterhin auf die Magnetisierung während der Relaxation ein und ermöglicht es ihr, sich auf kontrollierte Weise von ihrer instabilen Gleichgewichtsposition zu entfernen. So reicht es bei Impulsen mit einer Dauer von 10 ns aus, die Abfallzeit von 2 ns auf 4 ns zu erhöhen, um den Back-Switching-Effekt zu vermeiden.

Diese Lösung wurde an einer einzelnen SOT-MRAM-Speicherzelle demonstriert, bei der nach hunderttausenden kumulativen Schreibtests kein Schreibfehler mehr festgestellt wurde (WER < 2.10−6).

(a) Vergrößerung des Schreibfensters einer vereinfachten Speicherzelle (minimale WER) in Abhängigkeit von der Abfallzeit des elektrischen Impulses.

(b) Validierung dieser Lösung an einer vollständigen und funktionsfähigen Speicherzelle.

Über diese Ergebnisse hinaus ebnen diese Simulationen den Weg für Entwurfswerkzeuge für Speicherschaltkreise, die das Back-Switching berücksichtigen. Die nächsten Ziele für die industrielle Entwicklung dieser Technologie sind das Schreiben mit nur einem Strom sowie die Reduzierung dieses Stromes.