FX2LP contrôleur USB: CY7C68013 - Définition

La liste des auteurs de cet article est disponible ici.

Introduction

FX2LP est une appellation commerciale déposée par l'entreprise Cypress Semiconductor, couvrant une gamme de plusieurs microcontrôleurs conçus pour interfacer un système électronique avec un bus USB, typiquement pour rendre ce système électronique accessible depuis un ordinateur.

Il est fortement intégré et comprend :

- un émetteur récepteur USB 2.0

- un moteur d'interface série (SIE)

- un microprocesseur compatible Intel 8051

- une interface périphérique programmable (GPIF)

- une interface FIFO esclave

Datasheet

Disponible sur le site de Cypress : CY7C68013A/14A

Driver : CyUSB.sys

A l’installation de l’interface de communication CyConsole, le driver CyUSB.sys se trouve dans C:\Program Files\Cypress\USB DevStudio\Driver

Interface de communication : CyConsole

Pour communiquer avec un PC, il est nécessaire d’avoir une interface de communication, pour Windows c’est la CyConsole (Cypress USB Console), disponible sur le site de Cypress à partir de SuiteUSB 1.0 - USB Development tools for Visual C++ 6.0 (2) sous le nom USBDevStudio_1703.exe : CyConsole

Une fois installé une documentation illustrée présentant l’interface (Users’Guide) CyConsole.pdf est disponible dans C:\Program Files\Cypress\USB DevStudio\CyConsole

ATTENTION : Ne pas oublier de modifier le CyUSB.inf pour que le FX2LP soit reconnu (cf : Part 3 du Users’Guide)

Énumération

L’énumération est une étape qui permet d’identifier et de configurer le périphérique qui vient juste d’être branché sur le bus USB.

Pendant l’énumération le périphérique fournit à l’hôte (PC) une suite de descripteurs qui permettent son identification complète. L’hôte assigne une adresse unique au périphérique (adressage dynamique) et configure le périphérique.

Le FX2LP dispose déjà de l'énumération, aucun programme n'est nécessaire, on passe directement au transfert des données.

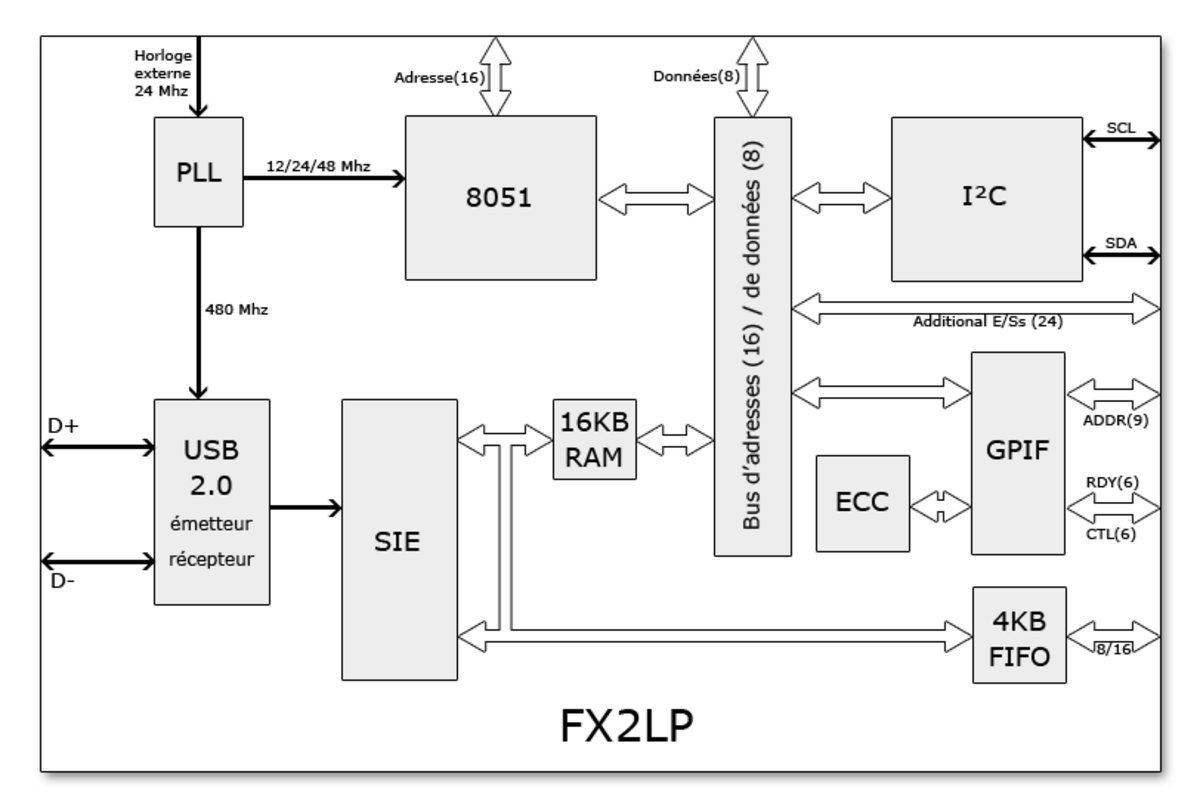

Schéma bloc

Plus précisément le FX2LP se compose de :

- 8051 : Microcontrôleur Intel

- SIE : Smart Interface Engine

- GPIF : General Programmable Interface

- FIFO : First In First Out

- I2C : Inter Integrated Circuit bus

- ECC : Error Correcting Codes

- USB2.0 : Transciever

- RAM : Random Access Memory

- PLL : Phase-Locked Loop

- Signaux externes

- D+/D- : reliés au connecteur USB

- Horloge externe : mettre un oscillateur de 24 MHz

- Adresses (16) / Données (8) : permet de connecter une mémoire externe

- SCL / SDA : permet d'ajouter une EEPROM I2C

- Additional I/O (24) : sert à programmer les interruptions, timers et USARTs du 8051

- Addresses (9) / RDY(6) / CTL(9) : signaux de contrôle du GPIF

- (8)/(16) : broches multiplexées

- → soit PB(8)+PD(8): ports d'entrée/sortie bidirectionnels

- → soit FD(16): bus de données bidirectionnel GPIF/FIFOS

- Différence entre les boîtiers (packages)

- 56 pins : Il lui manque le bus d’adresses et de données du microcontrôleur (permet de connecter une mémoire externe), il comprend uniquement 2 signaux RDY (ready) et 3 pour le CTL (control) du GPIF, il n’a pas de port E et C.

- Pour le Microcontrôleur, le 56 pins n’a pas accès aux 2 USARTs, aux 3 timers et aux 2 signaux d’interruption INT4 et INT5#.

- Le 56 pins est suffisant pour la majorité des applications USB.

- 100 pins : En plus du 56 pins, il comprend 4 signaux RDY et 3 CTL pour le GPIF, le port C et E. Il gère aussi les USARTs, timers, et interruptions.

- 128 pins : En plus du 100 pins, il a un bus d’adresses et de données pour utiliser une mémoire externe.

Le schéma bloc du FX2LP montre la version complète du composant (128 pins).

Le Microcontrôleur

C'est un Intel 8051 amélioré. Il comprend :

- 3 clocks possibles : 48 MHz, 24 MHz, ou 12 MHz

- 256 octets de RAM

- 3 timers/compteurs

- 2 USARTs

- un système d’interruptions étendu

- 2 pointeurs de données

- Son rôle

- Applique le protocole USB de niveau élevé en faisant des demandes de requêtes à l’hôte (PC), il s’occupe aussi du protocole I2C.

- Disponible sans reprogrammation, pour une utilisation standard du FX2LP.

- Ce n’est pas lui qui s’occupe du transfert USB (trop rapide pour lui), il sert à programmer l’interface, c’est les fifos qui vont s’occuper de transférer directement les données entre le FX2LP et l’interface externe.

Pour avoir plus de détails sur la configuration des registres et le fonctionnement du Microcontrôleur : EZ-USB TRM (Technical Reference Manual).

SIE

C'est un moteur d'interface intelligent (Smart Interface Engine) qui décode et encode les données sur D+/D-.

Il lit les signaux différentiels D+/D-, en extrait les données et envoie un paquet d'acquittement (ACK) pour signaler à l'hôte (PC) qu'il a bien reçu les données.

Il procède en sens inverse pour envoyer des données à l'hôte : il lit les données, les met au format USB et les envoie sur D+/D-.

GPIF

C'est une interface programmable (General Programmable Interface) qui permet de générer des signaux de contrôle (CTL), des adresses (GPIFADR) et des données (FD) pour commander un périphérique externe (ASICs, DSPs...).Il peut aussi attendre un évènement externe sur les broches RDY.

Ces signaux peuvent être programmés par l'utilisateur en modifiant les registres du 8051.

Ainsi le FX2LP fonctionne en mode Maitre (Master). Le GPIF peut être synchronisé par l'horloge interne (30/48 MHz) ou par une horloge externe sur IFCLK.

FIFO

I2C

Il est possible d’ajouter une EEPROM I2C. Sa fréquence de fonctionnement sera de 100 ou 400 kHz. L’EEPROM communique avec le 8051 par l’intermédiaire de 2 signaux SCL (clk) et SDA (données).

Le FX2LP gère automatiquement la mémoire I2C. Celle-ci est programmable par l'USB. Si le circuit détecte un boot loader (0xC0 ou 0xC2 sur le premier octet), alors il charge dans sa RAM, le programme contenu dans la mémoire I2C, puis l'exécute.

PLL

C’est une boucle à verrouillage de phase (Phase-Locked Loop), elle sert à multiplier ou diviser la fréquence (24 MHz) :

- pour le microcontrôleur 8051 :

- 24 MHz×2 = 48 MHz

- 24 MHz×1 = 24 MHz

- 24 MHz×0.5 = 12 MHz

- La valeur du registre CLKSPD1:0 détermine la fréquence d’utilisation du 8051.

- pour l’émetteur récepteur USB : 24 MHz×20 = 480 MHz