Pipeline (informatique) - Définition

La liste des auteurs de cet article est disponible ici.

Introduction

Un pipeline est un élément d'un circuit électronique dans lequel les données avancent les unes derrière les autres, au rythme du signal d'horloge. Dans la microarchitecture d'un microprocesseur, c'est plus précisément l'élément dans lequel l'exécution des instructions est découpée en étages. Le premier ordinateur à utiliser cette technique est l'IBM Stretch, conçu en 1958.

Définition

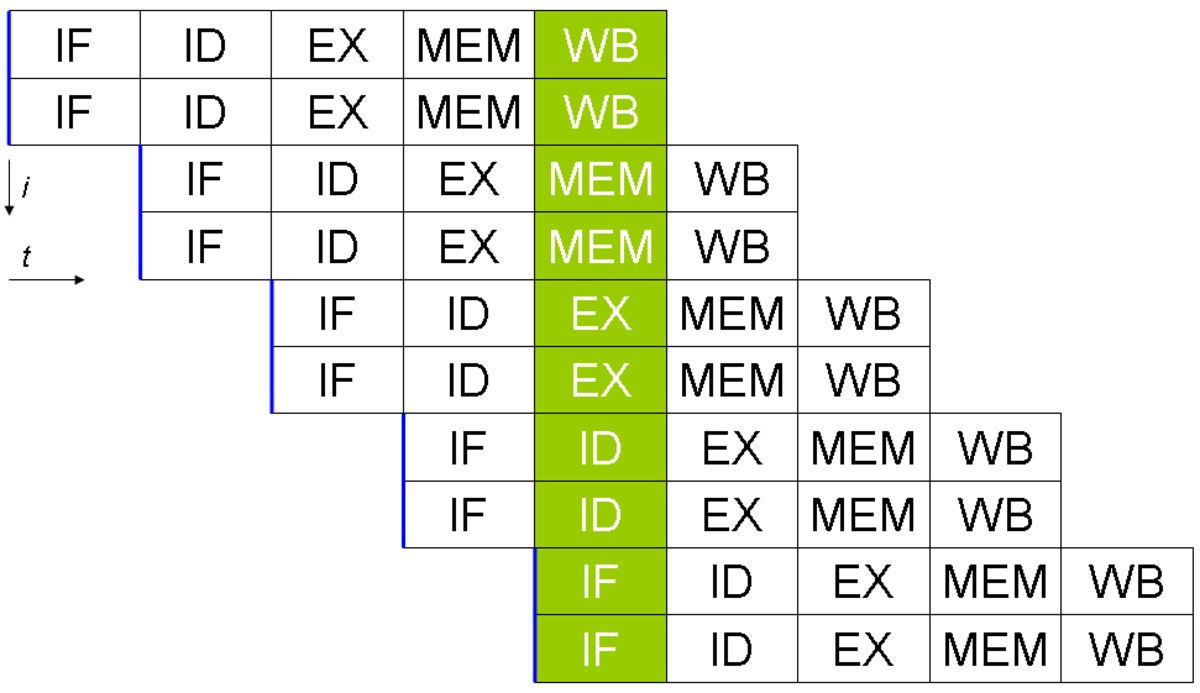

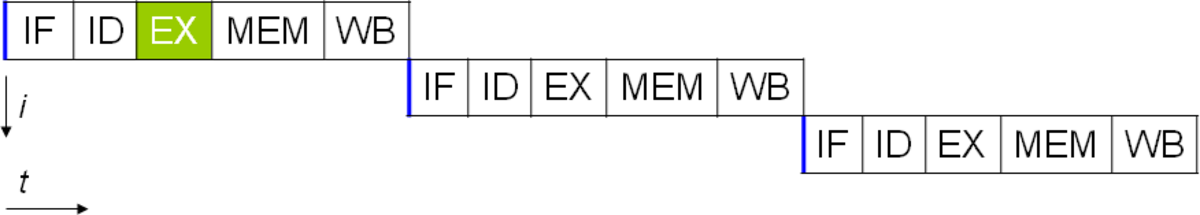

Soit un processeur où 5 cycles sont nécessaires pour accomplir une instruction :

- IF (Instruction Fetch) charge l'instruction à exécuter dans le pipeline.

- ID (Instruction Decode) décode l'instruction et adresse les registres.

- EX (Execute) exécute l'instruction (par la ou les unités arithmétiques et logiques).

- MEM (Memory), dénote un transfert depuis un registre vers la mémoire dans le cas d'une instruction du type STORE (accès en écriture) et de la mémoire vers un registre dans le cas d'un LOAD (accès en lecture).

- WB (Write Back) stocke le résultat dans un registre. La source peut être la mémoire ou bien un registre.

En supposant que chaque étape met 1 cycle d'horloge pour s'exécuter, il faut normalement 5 cycles pour exécuter une instruction, 15 pour 3 instructions :

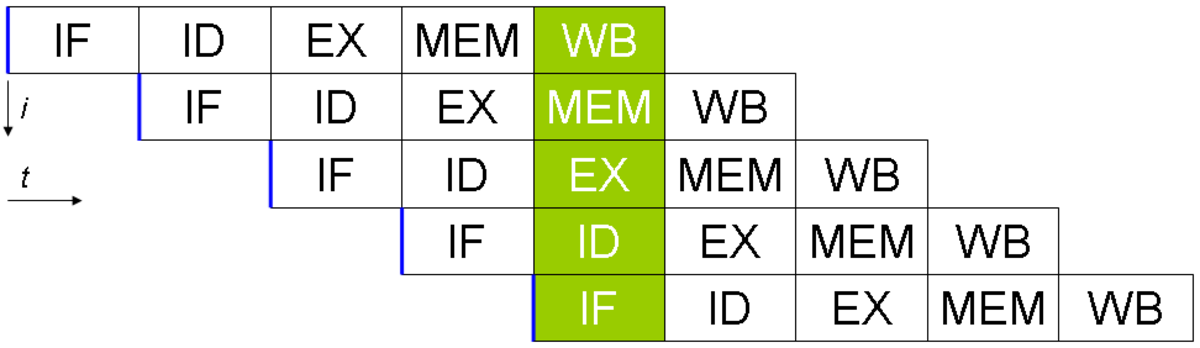

Si l'on insère des registres tampons (pipeline registers) entre chaque unité à l'intérieur du processeur, celui-ci peut alors contenir plusieurs instructions, chacune à une étape différente.

Les 5 instructions s'exécuteront en 9 cycles, et le processeur sera capable de terminer une instruction par cycle à partir de la cinquième, bien que chacune d'entre elles nécessite 5 cycles pour s'exécuter complètement.

Au 5e cycle, tous les étages sont en cours d'exécution.

Architecture superpipeline

Certaines architectures ont largement augmenté le nombre d'étages, celui-ci pouvant aller jusqu'à 31 pour la microarchitecture Prescott d'Intel. Une telle architecture sera appelée superpipelinée. Voici par exemple le pipeline des premiers Pentium 4, à 20 étages :

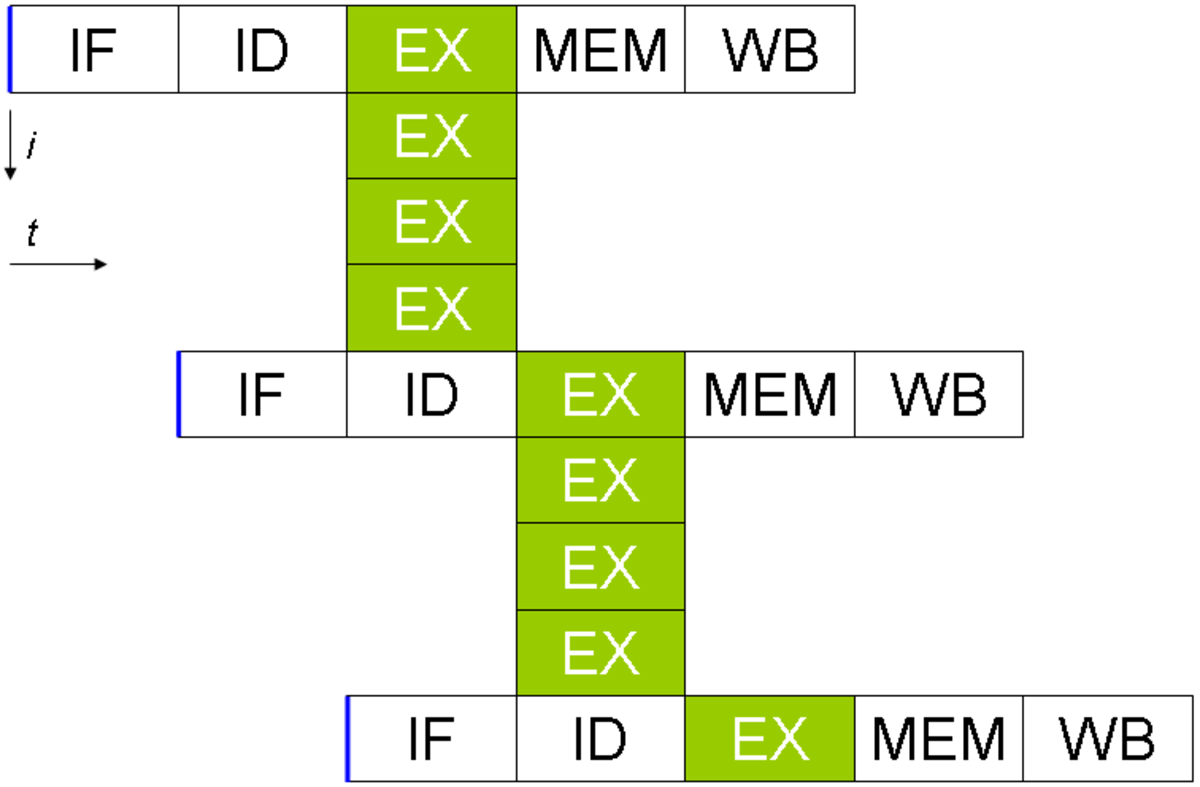

Architecture superscalaire

Une architecture superscalaire contient plusieurs pipelines en parallèle. Il est possible d'exécuter plusieurs instructions simultanément. Sur un processeur superscalaire de degré 2, deux instructions sont chargées depuis la mémoire simultanément. C'est le cas des processeurs récents conçus pour maximiser la puissance de calcul. Notons toutefois qu'en général, chaque pipeline est spécialisé dans le traitement d'un certain type d'instruction : aussi seules des instructions de types compatibles peuvent être exécutées simultanément.

Architecture VLIW

Dans les architectures VLIW (Very Long Instruction Word, ou Mot d'instruction très long), l'instruction va contenir les opérations pour chaque unité de calcul disponible dans le processeur. De ce fait chaque instruction peut être définie sur 256 bits, voire plus (512, 1024,...).