Cell (processeur) - Définition

La liste des auteurs de cet article est disponible ici.

Système

Annoncé le 29 juin 2005, le noyau du système d'exploitation Linux supportera ce processeur CELL : Annonce du port de Linux sur le processeur CELL - 29 juin 2005

On peut voir dans le ChangeLog, les changements intervenus pour la version 2.6.16 avec la précédente - 20 mars 2006 permettant à Linux de tourner à partir de cette version du noyau.

À partir de la version 2.6.16 du noyau Linux, vous pouvez consulter et utiliser la documentation du système de fichier virtuel de contrôle des SPUs en anglais.

Depuis le 14 juillet 2006, est accessible en anglais, en version SDK 1.1 et pour partie sous distribution Fedora core 5, l'ensemble des logiciels et documentation nécessaire au développement et à la compilation pour le processeur CELL sous Linux, cf. Informations about how to enable linux on Cell Broadband Engine™ based systems par (en) Barcelona Supercomputing Center (BSC).

L'accélération 3D libre pour le processeur CELL est ajouté en janvier 2008 avec une première version rudimentaire d'un pilote pour Gallium 3D le futur remplaçant de Mesa 3D, implémentation libre d'OpenGL. .

Architecture

Il dispose de 234 millions de transistors gravés sur une surface de 235 mm2 en 90 nm SOI (Silicon On Insulator). La version finale tourne à 3,2 GHz en 0,9 V et est formée de huit couches de cuivre interconnectées. Le contrôle de la température est dynamique : dix capteurs thermiques numériques et un capteur linéaire.

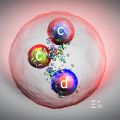

Un processeur CBE (Cell Broadband Engine) est composé de :

- 1 PPE (PowerPC Processing Element) : unité généraliste simplifiée, « in order »

- 8 SPEs (Synergistic Processing Element) ou « SIMD processing unit » pour certains auteurs

- Un cache de niveau 2 de 512 Ko partagé

- l'EIB (Element Interconnect Bus) qui gère les communications internes entre les différents éléments

- MIC (Memory Interface Controler) : contrôleur mémoire partagé

- Flex I/O interface : contrôleur d'entrées/sorties (E/S)

Le mot cell signifie cellule en anglais. Le processeur se décompose en effet en plusieurs cellules. Une cellule est un ensemble formé par le PPE et un SPE. Cette unité matérielle indépendante peut être affectée à un thread. La répartition des tâches selon les cellules est l'enjeu pour le programmeur qui souhaite utiliser au mieux ce processeur.

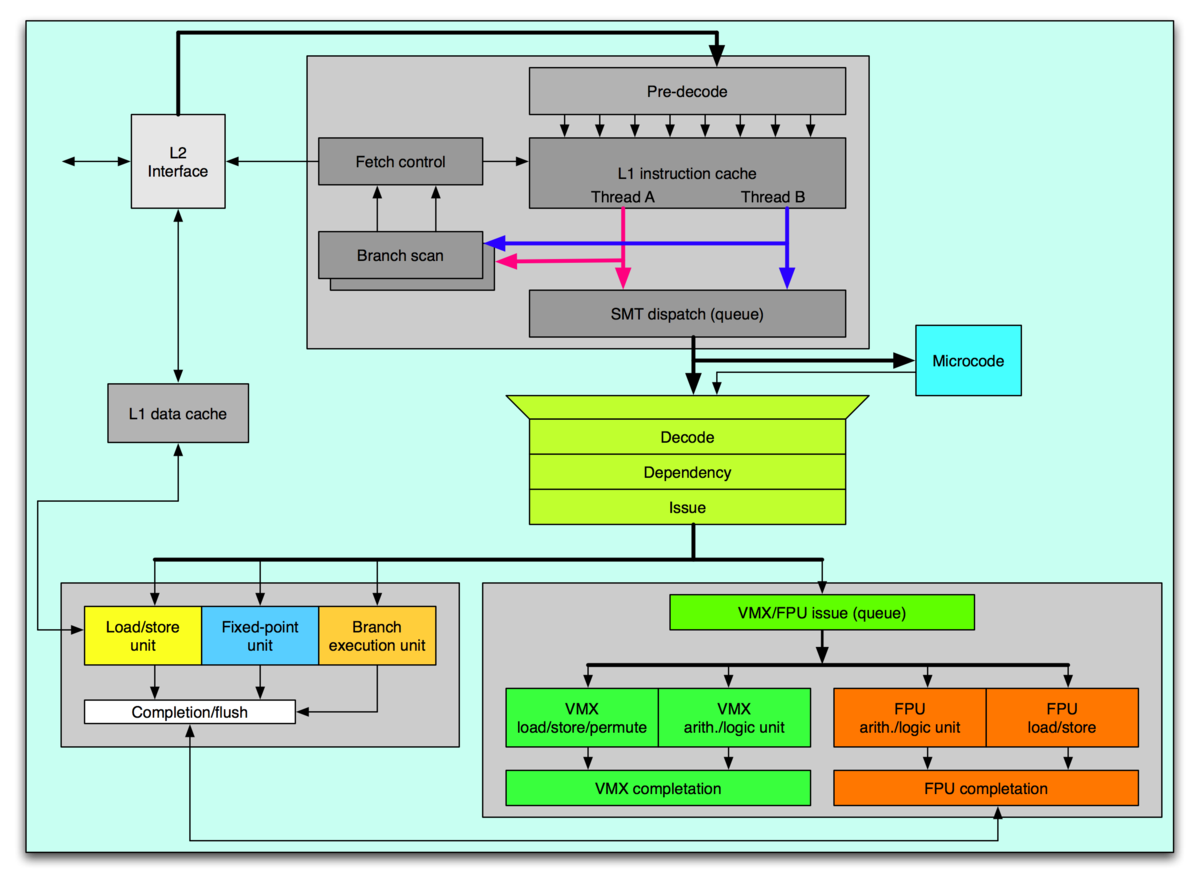

Le PowerPC Processing Element

Le cœur (PPE) utilise les jeux d'instructions IBM POWER et AltiVec, les nombres entiers, et la répartition du travail entre les SPEs. C'est un processeur 64 bits, « In Order », et SMT deux voies. Il a une mémoire cache intégrée de niveau 1 de 32 Ko.

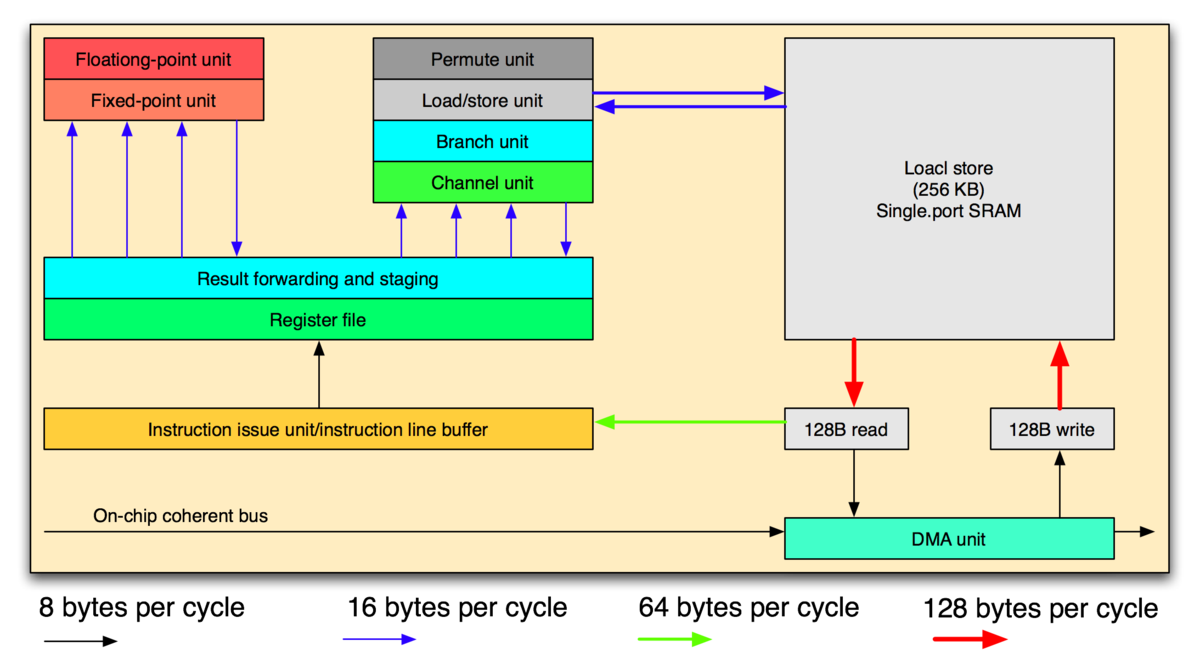

Les Synergistic Processing Element

Ils se destinent au calculs SIMD. Un SPE correspond à un processeur vectoriel indépendant possédant 128 registres 128 bit, 4 unités de calcul en virgule flottante double précision et 4 unités de calcul entiers. Il effectue deux instructions par cycle d'horloge. Il inclut une mémoire locale de 256 Ko de type SRAM haute vitesse. Un processeur Cell contient 8 SPEs.

Celui de la PS3 n'aura que 7 unités fonctionnelles. Les différentes hypothèses à ce sujet sont :

- limiter le nombre de rejet en sortie d'usine ;

- gérer les DRMs et de la sécurité ;

- garantir le fonctionnement de la PS3 en cas de défaillance matérielle d'un cœur durant la durée de vie de la console.

L'Element Interconnect Bus

Comporte 4 boucles 128 bit supportant des transferts multiples. Il relie tous les composants du CELL entre eux : PPE, SPEs, cache L2 et contrôleurs mémoire et entrées/sorties.

Contrôleurs mémoire et entrée/sortie

Le MIC est un double contrôleur mémoire XDR (XDRAM) offrant un débit de 25,6 Go par seconde. On trouve deux interfaces E/S configurables (76,8 Go/s, 6,4 Gbit/s) (Flexible I/O)