Cell (processeur) - Définition

La liste des auteurs de cet article est disponible ici.

Introduction

Le Cell est un processeur conçu conjointement par IBM, Sony et Toshiba, révélé en février 2005. Il équipe notamment la console de jeu vidéo PlayStation 3 de Sony. Il est envisagé de produire également des ordinateurs à base de Cell chez IBM, Mercury Computer Systems et Toshiba (Qosmio F50/55 et G50/55).

Ses champs de prédilection, appliqués aux calculs vectoriels à virgule flottante, sont :

- le jeu vidéo avec la console PlayStation 3 et les bornes d'arcade (Namco Bandai)

- les applications multimédia, films, TVHD (Sony, Toshiba)

- le rendu en temps réel, les simulations physiques, le traitement du signal (DSP)

- l'imagerie médicale, l'aérospatial et la défense, le calcul sismique, les télécommunications

Philosophie

Il est important de comprendre, au-delà des chiffres avancés par les concepteurs, la philosophie du Cell, radicalement différente des autres processeurs qui équipent, par exemple, les PC comme le Phenom d’AMD ou le Core 2 d’Intel.

Moins de complexité pour plus de puissance brute

En effet, les processeurs traditionnels ont développé ces dernières années, en amont des unités d'exécutions proprement dites, des unités d'optimisation du code informatique composant les programmes. Ceci facilite grandement la tâche des programmeurs, et un code non optimisé peut fonctionner dans de bonnes conditions. À titre d'exemple, les processeurs traditionnels réorganisent le code en interne avant exécution, ils sont dits « OoO » (out of order). Les instructions peuvent être exécutées dans un ordre différent de celui donné par le programme. Après exécution, le processeur remet les instructions dans le bon ordre pour garantir le bon fonctionnement. Cela implique de plus un matériel de suivi (de traçabilité) des instructions au fur et à mesure de leur progression dans le pipeline. Tout ce travail consomme énormément de place (de transistors) sur le processeur.

Enfin, les processeurs traditionnels n'évoluent plus fondamentalement depuis des années. Ils se contentaient essentiellement d'exploiter les nouveaux procédés de gravure pour monter en fréquence. Cette ère est terminée depuis le 90 nm, qui ne permet plus de monter en fréquence autant que par le passé. C'est pour cette raison que l'on assiste à l'émergence des processeurs double cœur : on exploite la nouvelle finesse de gravure pour mettre plus de transistors et développer le SMP à l'intérieur même du processeur, sans grande augmentation de fréquence.

IBM pour le Cell a choisi une approche originale. Le Cell, tout comme les processeurs du passé, ne fait aucun travail de réorganisation du code, il est dit « in order ». Cela libère beaucoup de place pour ajouter de nouvelles unités d'exécution. L'inconvénient est que le travail d'optimisation est à la charge du programmeur et du compilateur et nuit donc à l'interopérabilité. Le déplacement d'un travail à l'extérieur du processeur avait déjà prévalu pour le RISC.

Une autre originalité du Cell, c'est qu'il est optimisé pour le calcul parallèle : plusieurs processeurs peuvent communiquer entre eux et partager leur charge de travail. Ainsi, plus on possède de processeurs Cells, plus on a une puissance de calcul importante à disposition.

Les performances maximales théorique (peak) du processeur Cell @3,2 GHz avec 8 SPEs, atteintes lors de calculs vectoriels, sont :

- en simple précision 32 bits (SP) : 230,4 GFLOPS (25,6 GFLOPS par SPE, 25.6 GFLOPS pour le PPE)

- en double précision 64 bits (DP) : 20,8 GFLOPS (1.8 GFLOPS par SPE, 6.4 GFLOPS pour le PPE)

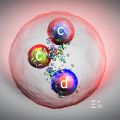

Un cœur principal et huit cœurs spécifiques

Plutôt que de dupliquer plusieurs fois le même cœur identique, comme sur les processeurs multi cœur classiques, les concepteurs ont choisi une toute autre approche : 1 cœur principal, et 8 cœurs spécifiques.

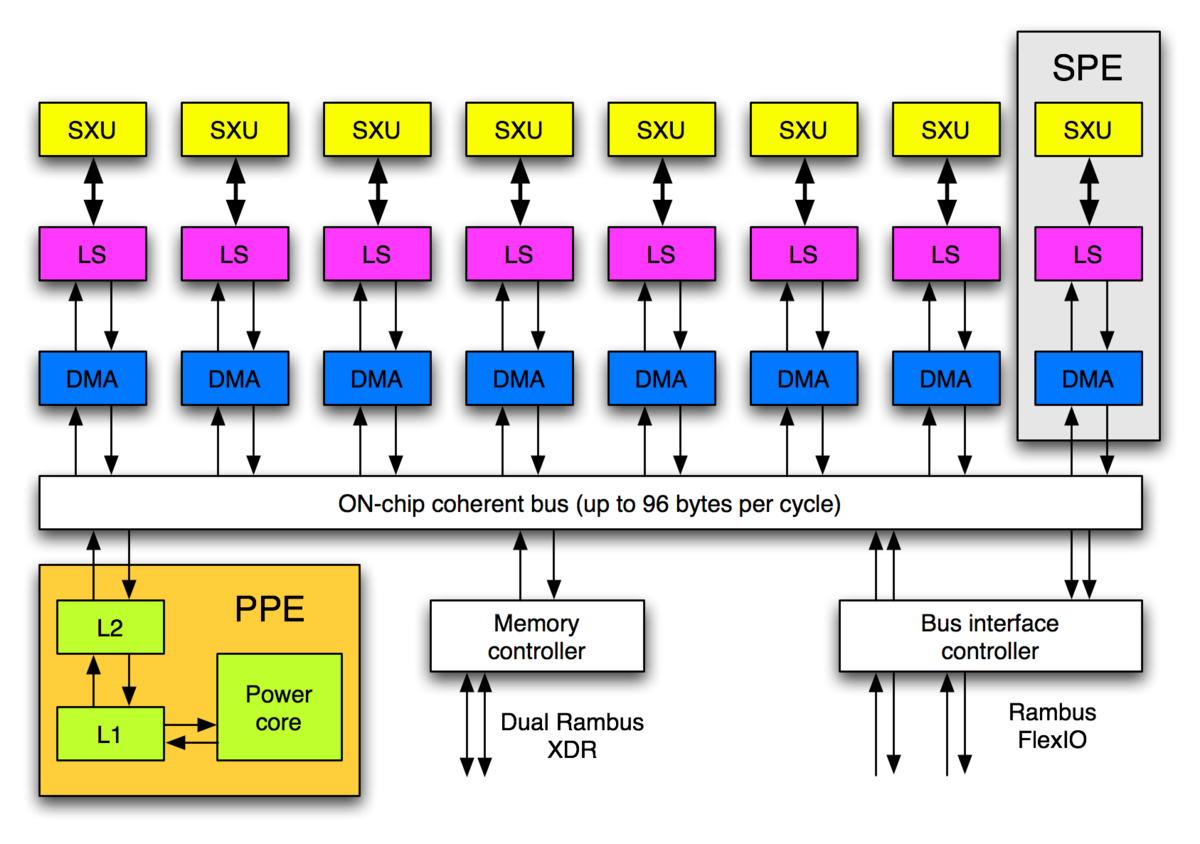

Le cœur principal, dit PowerPC Processing Element ou PPE, reste relativement proche d'un cœur classique : même si comme nous l'avons vu sa conception est simplifiée, en particulier avec l'absence de module d'optimisation, le jeu d'instruction IBM POWER, bien connu, permet un accès à la RAM via un système de cache à deux niveaux L1 et L2. Ainsi, le PPE est la partie du Cell la moins exotique.

Chacun des 8 cœurs spécifiques, dit Synergystic Processing Elements ou SPE, est constitué de 2 parties : une mémoire locale (Local Storage ou LS) de 256 Ko et une unité de calcul vectoriel dite Streaming Processor Unit ou SPU. Dotés d'un jeu d'instruction SIMD spécifique mais se rapprochant de AltiVec, les SPU ont un accès direct et extrêmement rapide à leur mémoire locale. Par contre, pour accéder à la mémoire principale ils doivent effectuer une requête de transfert asynchrone à un bus d'interconnexion.

Ce bus d'interconnexion dit Element Interconnect Bus ou Bus EIB est le dernier élément très important du Cell. Son rôle est d'établir la connexion entre le PPE, les SPE, la mémoire RAM principale, et les périphériques d'entrée-sortie.

Pour résumer et simplifier :

- le PPE se charge de préparer le travail et de démarrer les SPE (c'est un peu un rôle de chef d'orchestre). Il sert aussi à effectuer toutes les tâches qui ne peuvent pas simplement être effectuées sur les SPE.

- Les SPE exécutent ainsi les calculs les plus complexes à la demande du PPE en récupérant les données dans leur mémoire locale grâce à l'EIB.

- Enfin, pour maximiser les performances en évitant d'attendre l'EIB, le code s'exécutant sur un SPU doit effectuer ses calculs en même temps qu'ont lieu les transferts, par exemple en utilisant plusieurs mémoires tampons.