Mode protégé - Définition

La liste des auteurs de cet article est disponible ici.

Pagination

La segmentation ne pouvant être désactivée, les adresses virtuelles sont systématiquement traitées par l'unité de segmentation, qui produit une adresse linéaire. Lorsque la pagination n'est pas disponible (80286) ou désactivée, cette adresse linéaire est directement considérée comme une adresse physique. Cependant, le 80386 et ses successeurs offrent un puissant mécanisme de pagination qui permet de gérer très efficacement la mémoire virtuelle.

Dans le cas le plus fréquent, la mémoire virtuelle (celle correspondant aux adresses linéaires) est divisée en pages de 4 Kio (mais il est possible également d'avoir des pages de 2 Mio ou 4 Mio). Chaque contexte dispose d'un espace d'adressage de 4 Gio, soit 1 024×1 024 pages, dont certaines d'entre elles correspondent à des cadres en mémoire physique (qui ont la même taille, donc habituellement 4 Kio). L'association entre pages et cadres est assurée par l'unité de pagination.

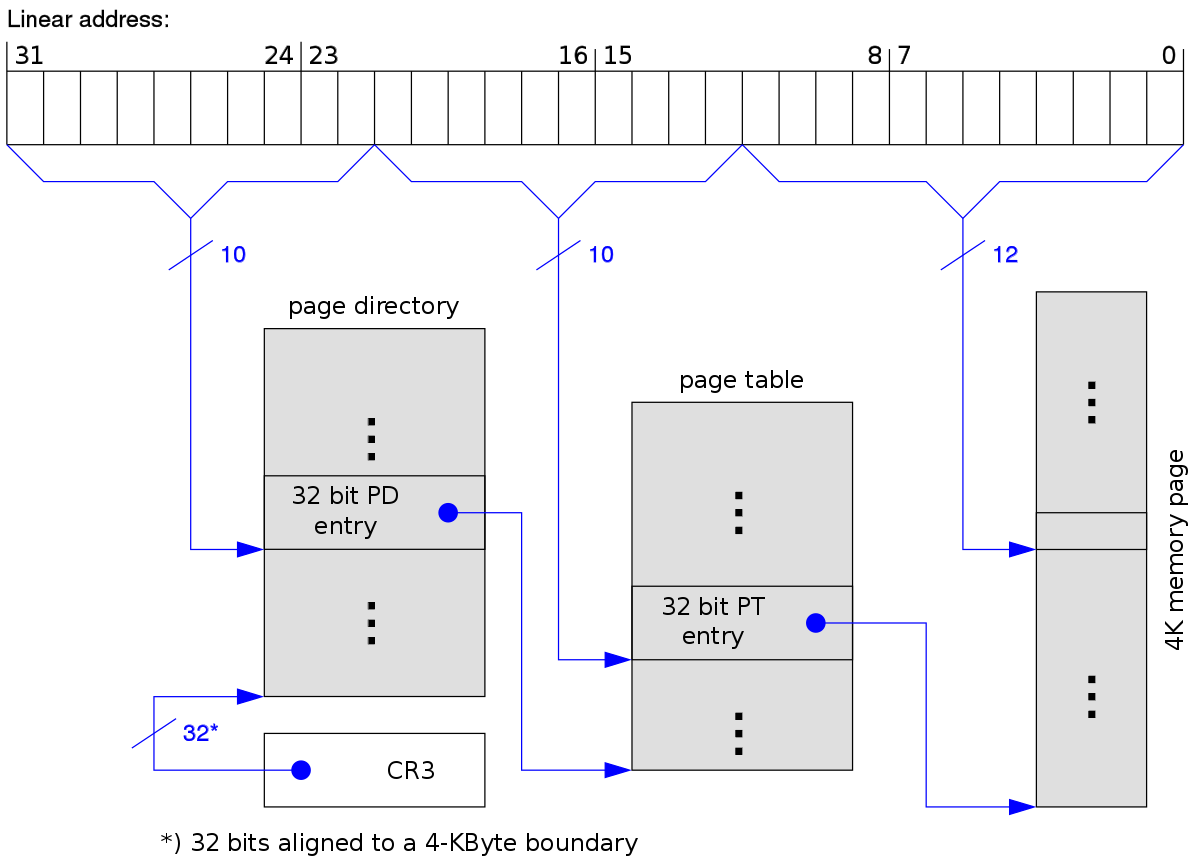

Afin de limiter la taille de la table des pages (a priori un tableau de plus d'un million d'entrées, mais très creux), une structure à deux niveaux est mise en place :

- les 10 bits de poids plus fort de l'adresse permettent de désigner une entrée d'un répertoire de tables de pages (dont l'adresse de base est donnée par le registre CR3), qui compte donc 1 024 entrées de 32 bits chacune (soit 4 Kio, soit exactement un cadre. Cette entrée donne l'adresse d'un cadre qui contient un tableau de deuxième niveau, la table de pages ;

- les 10 bits suivants de l'adresse désignent une entrée de cette table de pages. Cette dernière compte donc également 1 024 entrées, de 32 bits chacune, soit exactement un cadre ici aussi. Cette entrée donne l'adresse (physique) du cadre associé à la page ;

- les 12 bits de poids faible donnent le déplacement, aussi bien dans la page que dans le cadre.

Une entrée de répertoire ou de table de pages fait 32 bits, or une adresse de cadre est donnée sur 20 bits (10+10). Il reste donc 12 bits supplémentaires, qui correspondent à divers indicateurs, dont le bit de présence, qui indique que la page n'est pas présente en mémoire. Lorsque cela se produit, une exception de type défaut de page est levée, et doit être traitée par le système d'exploitation. Deux cas se présentent :

- la page en question a précédemment été stockée sur une mémoire de masse pour libérer de la mémoire physique (swap). Il faut donc à nouveau libérer de la mémoire physique le cas échéant, et rapatrier la page de la mémoire de masse vers la mémoire centrale avant que le processus puisse poursuivre son exécution ;

- la page n'a pas été allouée par le processus : celui-ci vient donc de provoquer une erreur, et doit être terminé.

Les modes protégés de x86-64

Le mode 32 bits de x86 est conservé, appelé Legacy Mode (mode hérité). x86-64 introduit un autre mode protégé en 64 bits natif appelé Long mode, avec des différences notables :

- Sous-mode de compatibilité pour exécuter des programmes compilés en 32 ou 16 bits utilisant le mode protégé

- Taille de page de 4 Kio ou 2 Mio

- Disparition quasi-totale de la segmentation (mémoire virtuelle adressée par 64 bits à plat). CS, DS, FS et SS sont traités comme s'ils valaient zéro. FS et GS ont un traitement particulier.

- Désactivation du mode virtuel 8086

- Disparition du basculement de tâches automatique. La commutation de contexte incombe désormais au logiciel.

- Nouvelle manière de changer le niveau de privilège